|

||||||||||||||||||||||||||||||||||||||||||||||||

![]()

|

Logique et addition Comment réaliser un

additionneur Explications pas à

pas |

|

|

||

|

|

1 bit + 1 bit: 0 + 0 = 0 0 + 1 = 1 1 + 0 = 1 1 + 1 = 10 On se souvient que 10 binaire vaut 2 en décimal. Addition

en binaire: 5 + 6 5 = 1x4 + 0x2

+ 1 =>

1 0 1 6 = 1x4 + 1x2

+ 0 =>

1 1 0 Somme bit à bit: 1 0 1 1 Vérification du résultat: 1x8 + 0x4 + 1x2 + 1 = 11 qui est bien égal à 5 + 6. Addition

en binaire: 5 + 7 5 = 1x4 + 0x2

+ 1 =>

1 0 1 7 = 1x4 + 1x2

+ 1 =>

1 1 1 Somme bit à bit: 1 1 0 0 Vérification du résultat: 1x8 + 1x4 + 0x2 + 0 = 12 qui est bien égal à 5 + 7. |

|

|

appelé: demi-additionneur |

|

|||||||||||||||||||||

|

Table

de vérité de l'addition de 1 bit (A) + 1 bit

(B):

Note: on dit table de vérité, car en logique le "1" est assimilé à

"vrai" et le "0" à "faux". |

Analyse

de la table de vérité La colonne somme correspond à la fonction logique

"ou exclusif" et la colonne de la

retenue correspond à la fonction logique "et" avec une porte OU exclusif et une porte ET.

|

|||||||||||||||||||||

|

|

||||||||||||||||||||||||||||||||||||||||||||||

|

Table

de vérité de l'addition de 1 bit (A) + 1 bit

(B) + retenue (C)

|

||||||||||||||||||||||||||||||||||||||||||||||

Anglais: retenue se dit: Carry (d'où le C pour son symbole)

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

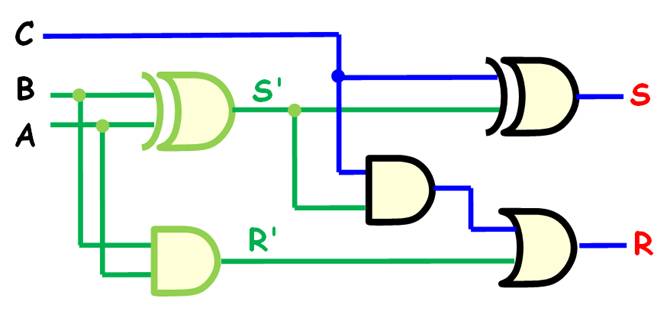

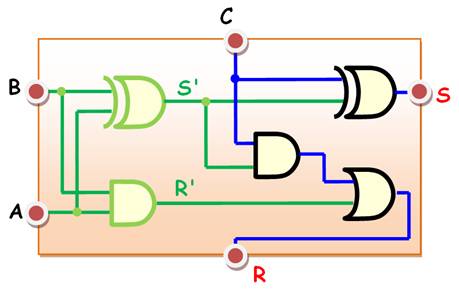

S = A

R = R' ou S' et C

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Voir

Simplification avec Karnaugh

|

|

|

|

S = A R = R' ou S' et C

Auquel, on ajoute le traitement de la retenue (C,

circuit en bleu). Pour cela, il nous faut ajouter un ou

exclusif entre C et S'; un et entre C

et S'; et, un ou entre ce résultat et R'.

|

|

|

|

||

|

|

||

|

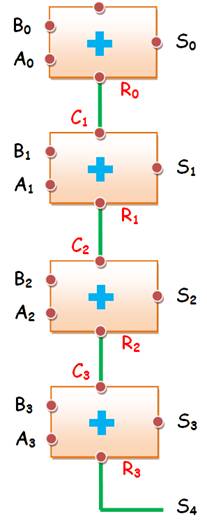

Pour ajouter

Le résultat est:

|

|

|

|

|

|

|

|

|

![]()

|

Suite |

|

|

Voir |

|

![]()